## Hardware data sheet section III addendum

# ET1810 / ET1811 / ET1812 and ET1815 / ET1816

# Ether CAT. Slave Controller IP Core for Altera, and AMD, FPGAs

Section I - Technology

(Online at <a href="http://www.beckhoff.com">http://www.beckhoff.com</a>)

Section II – Register Description

(Online at <a href="http://www.beckhoff.com">http://www.beckhoff.com</a>)

Section III – Hardware Description

(Online at <a href="http://www.beckhoff.com">http://www.beckhoff.com</a>)

Section III - Addendum

Design flow compatibility, FPGA device support, known issues

Version 3.2

Date: 2024-03-13

#### **DOCUMENT ORGANIZATION**

The Beckhoff EtherCAT Slave Controller (ESC) documentation covers the following Beckhoff ESCs:

- ET1200

- ET1100

- EtherCAT IP Core for Altera® FPGAs

- EtherCAT IP Core for AMD® (Xilinx)® FPGAs

The documentation is organized in three sections. Section I and section II are common for all Beckhoff ESCs, Section III is specific for each ESC variant.

The latest documentation is available at the Beckhoff homepage (http://www.beckhoff.com).

#### Section I - Technology (All ESCs)

Section I deals with the basic EtherCAT technology. Starting with the EtherCAT protocol itself, the frame processing inside EtherCAT slaves is described. The features and interfaces of the physical layer with its two alternatives Ethernet and EBUS are explained afterwards. Finally, the details of the functional units of an ESC like FMMU, SyncManager, Distributed Clocks, Slave Information Interface, Interrupts, Watchdogs, and so on, are described.

Since Section I is common for all Beckhoff ESCs, it might describe features which are not available in a specific ESC. Refer to the feature details overview in Section III of a specific ESC to find out which features are available.

#### Section II - Register description (All ESCs)

Section II contains detailed information about all ESC registers. This section is also common for all Beckhoff ESCs, thus registers, register bits, or features are described which might not be available in a specific ESC. Refer to the register overview and to the feature details overview in Section III of a specific ESC to find out which registers and features are available.

#### Section III - Hardware description (Specific ESC)

Section III is ESC specific and contains detailed information about the ESC features, implemented registers, configuration, interfaces, pinout, usage, electrical and mechanical specification, and so on. Especially the Process Data Interfaces (PDI) supported by the ESC are part of this section.

#### Additional documentation

Application notes and utilities can also be found at the Beckhoff homepage. Pinout configuration tools for ET1100/ET1200 are available. Additional information on EtherCAT IP Cores with latest updates regarding design flow compatibility, FPGA device support and known issues are also available.

#### Trademarks

Beckhoff®, TwinCAT®, TwinCAT/BSD®, TC/BSD®, EtherCAT®, EtherCAT G®, EtherCAT G10®, EtherCAT P®, Safety over EtherCAT®, TwinSAFE®, XFC®, XTS® and XPlanar® are registered trademarks of and licensed by Beckhoff Automation GmbH. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

#### **Patent Pending**

The EtherCAT Technology is covered, including but not limited to the following patent applications and patents: EP1590927, EP1789857, EP1456722, EP2137893, DE102015105702 with corresponding applications or registrations in various other countries.

#### Disclaimer

The documentation has been prepared with care. The products described are, however, constantly under development. For that reason, the documentation is not in every case checked for consistency with performance data, standards or other characteristics. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made on the basis of the data, diagrams and descriptions in this documentation.

#### Copyright

© Beckhoff Automation GmbH & Co. KG 03/2024.

The reproduction, distribution and utilization of this document as well as the communication of its contents to others without express authorization are prohibited. Offenders will be held liable for the payment of damages. All rights reserved in the event of the grant of a patent, utility model or design.

#### **DOCUMENT HISTORY**

| Version | Comment                                                                                                                                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | Initial release                                                                                                                                                                                                                                      |

| 1.1     | Update to EtherCAT IP Core V3.0.2/V3.00c                                                                                                                                                                                                             |

| 1.2     | Update to EtherCAT IP Core V2.4.3/V2.04d                                                                                                                                                                                                             |

| 1.3     | Update to Altera Quartus 13.0 SP1 and Xilinx Vivado 2013.2                                                                                                                                                                                           |

| 1.4     | Update to Altera Quartus 13.1, Xilinx Vivado 2013.3, and ISE14.7                                                                                                                                                                                     |

| 1.5     | <ul> <li>Update to EtherCAT IP Core V3.0.5/V3.00f</li> <li>Update to Xilinx Vivado 2013.4, editorial changes</li> </ul>                                                                                                                              |

| 1.6     | <ul> <li>Update to EtherCAT IP Core V3.0.6/V3.00g</li> <li>Update to Xilinx Vivado 2014.1</li> </ul>                                                                                                                                                 |

| 1.7     | <ul> <li>Update to Altera Quartus 14.0, Xilinx Vivado 2014.2</li> <li>Added Altera MAX10, Xilinx Kintex UltraScale, and Virtex UltraScale</li> </ul>                                                                                                 |

| 1.8     | <ul> <li>Update to EtherCAT IP Core V3.0.9/V3.00j</li> <li>Update to Xilinx Vivado 2014.3</li> <li>Added known design flow issues chapters</li> </ul>                                                                                                |

| 1.9     | Update to EtherCAT IP Core V3.0.9 Patch 1/V3.00j Patch 1                                                                                                                                                                                             |

| 2.0     | <ul> <li>Update to EtherCAT IP Core V2.4.4/V2.04e and V3.0.10/V3.00k</li> <li>Update to Altera Quartus 14.1, Xilinx Vivado 2014.4</li> <li>Added Altera Arria 10</li> </ul>                                                                          |

| 2.1     | Update to Altera Quartus 15.0, Xilinx Vivado 2015.1                                                                                                                                                                                                  |

| 2.2     | Update to Xilinx Vivado 2015.2                                                                                                                                                                                                                       |

| 2.3     | <ul> <li>Update to Altera Quartus Prime 15.1, Xilinx Vivado 2015.3 and 2015.4</li> <li>Removed issue "Tristate drivers are not properly connected" with Arria 10, because it produces only a warning, while the implementation is correct</li> </ul> |

| 2.4     | Update to Xilinx Vivado 2016.1                                                                                                                                                                                                                       |

| 2.5     | Update to Altera Quartus Prime Standard/Pro 16.0                                                                                                                                                                                                     |

| 2.6     | <ul> <li>Added Vivado 2016.1 known issue "Synthesis fails with an RTL assertion error"</li> <li>Update to Xilinx Vivado 2016.2</li> <li>Update to Altera Quartus Prime Standard/Pro 16.0.1</li> </ul>                                                |

| 2.7     | <ul> <li>Replaced Altera by Intel</li> <li>Update to EtherCAT IP Core V3.0.10 Patch 1/V3.00k Patch 1</li> <li>Update to Intel Quartus 16.1, Xilinx Vivado 2016.4</li> <li>Added Xilinx Zynq UltraScale+</li> <li>Added MD5 checksums</li> </ul>      |

| 2.8     | <ul> <li>Update to Intel Quartus 17.0, Xilinx Vivado 2017.1</li> <li>Added Intel Cyclone 10 GX and LP</li> <li>Added Xilinx Spartan-7</li> </ul>                                                                                                     |

| 2.9     | <ul> <li>Update to Intel Quartus 17.1-18.0</li> <li>Update to Xilinx Vivado 2017.2-2018.2</li> <li>Update known issues</li> </ul>                                                                                                                    |

| 3.0     | <ul> <li>Update to EtherCAT IP Core V3.0.10 Patch 2/V3.00k Patch 2</li> <li>Update to Intel Quartus Prime Standard 18.1, Quartus Prime Pro 19.1</li> <li>Update to Xilinx Vivado 2019.1</li> </ul>                                                   |

| 3.1     | <ul> <li>Update to EtherCAT IP Core V3.0.10 Patch 3/V3.00k Patch 3</li> <li>Update to Intel Quartus Prime Standard 19.1</li> </ul>                                                                                                                   |

BECKHOFF New Automation Technology

CONTENTS

| Version | Comment                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2     | <ul> <li>Replaced Intel by Altera, replaced Xilinx by AMD</li> <li>Update to AMD Vivado/Vitis 2023.2</li> <li>Added AMD Artix Ultra-Scale+, Versal Al Core/Edge/HBM/Prime/Premium</li> <li>Update to Altera Quartus Prime 23.1/Quartus Prime Pro 23.4</li> <li>Added Altera Cyclone 10 GX, Stratix 10, and Agilex 5/7 support</li> <li>Corrected Altera Stratix 10 license support</li> </ul> |

## CONTENTS

| 1 | Overview   |                |             |                                                                                                                                                                           |          |

|---|------------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2 | EtherCAT I | P Core fo      | r Altera FF | PGAs                                                                                                                                                                      | 2        |

|   | 2.1        | FPGA d         | esign tool  | compatibility                                                                                                                                                             | 2        |

|   | 2.2        | FPGA d         | evice com   | patibility                                                                                                                                                                | ;        |

|   | 2.3        | FPGA d         | evice licer | nse support                                                                                                                                                               | 4        |

|   | 2.4        | Known          | design flov | v issues                                                                                                                                                                  | į        |

|   |            | 2.4.1<br>23.4) | Active (a   | at least until Quartus Prime Standard 23.1/Quartus Prime Pro                                                                                                              |          |

|   |            |                | 2.4.1.1     | Quartus Prime 21.1 – today: DE2_115 example designs are missing component altera_avalon_lcd_16207                                                                         | į        |

|   |            |                | 2.4.1.2     | Quartus Prime Pro – today: Critical warnings about ignored initial state in some state machines                                                                           |          |

|   |            |                | 2.4.1.3     | Quartus Prime Pro 17.0 – today: Upgrade to Qsys Pro/Platfo<br>Designer Pro fails due to missing simulation support                                                        | rmc<br>; |

|   |            |                | 2.4.1.4     | Quartus Prime Standard/Pro 16.1 – today: Windows setup d not integrate the EtherCAT IP Core into the Quartus IP catal                                                     |          |

|   |            |                | 2.4.1.5     | Quartus 14.0 – today: Cyclone III example designs are not synthesizable                                                                                                   | (        |

|   |            |                | 2.4.1.6     | TimeQuest with EtherCAT IP Core V3.0.x: Recovery timing violation inside the EtherCAT IP Core from 25 MHz rising ed to 100 MHz falling edge (5 ns)                        | ge<br>(  |

|   |            |                | 2.4.1.7     | Qsys with EtherCAT IP Core V2.x.x: Avalon read error                                                                                                                      | (        |

|   |            | 2.4.2          | Solved      |                                                                                                                                                                           | -        |

|   |            |                | 2.4.2.1     | EtherCAT IP Core before V3.0.10 Patch 3: DE2-115 NIOS RGMII example design is missing a register for DDR input signals                                                    |          |

|   |            |                | 2.4.2.2     | Quartus Prime Standard 16.0 – today with EtherCAT IP Core before V3.0.10 Patch 3: DE2-115 MII/RGMII example design synthesis fails because of an additional ALTPLL signal |          |

|   |            |                | 2.4.2.3     | Quartus 14.0 – today with EtherCAT IP Core before V3.0.10 Patch 1: Cyclone IV DBC4CE55 with NIOS example design PLL cannot be upgraded or edited                          | -        |

|   |            |                | 2.4.2.4     | MAX10 with EtherCAT IP Core V2.4.0 – V3.0.10 Patch 1: So configuration modes are not possible with EtherCAT IP Core memory initialization                                 |          |

|   |            |                | 2.4.2.5     | Quartus Prime Pro 16.0 – 21.3: Assertions and report messages are not evaluated                                                                                           | 8        |

|   |            |                | 2.4.2.6     | Quartus Prime Standard 16.0.0: DE2-115 MII/RGMII example designs: ALTPLL cannot be generated                                                                              | le {     |

|   |            |                | 2.4.2.7     | Quartus 14.0: EtherCAT IP Core V3.0.0-V3.0.6: DE2-115 example designs are not working                                                                                     | 8        |

|   | 2.5        | MD5 Ch         | necksums    |                                                                                                                                                                           | 9        |

| 3 | EtherCAT I | P Core fo      | r AMD FP    | GAs                                                                                                                                                                       | 1        |

|   | 3.1        | Vivado/        | Vitis desig | n tool compatibility                                                                                                                                                      | 1        |

|   | 3.2        | EDG9 4         | evice com   | natihility                                                                                                                                                                | 13       |

BECKHOFF New Automation Technology

CONTENTS

| 3.3 | Known \  | /ivado des | sign flow issues                                                                                                           | 13        |

|-----|----------|------------|----------------------------------------------------------------------------------------------------------------------------|-----------|

|     | 3.3.1    | Active (a  | it least until Vivado 2023.2)                                                                                              | 13        |

|     |          | 3.3.1.1    | Vitis 2023.2 – today: ZC702 AXI Vivado example design software application template is not supported anymore               | 13        |

|     |          | 3.3.1.2    | Vivado 2020.1 – today: ZC702 AXI Vivado example design hunassigned addresses for block design components                   | as<br>13  |

|     |          | 3.3.1.3    | Vivado 2016.1 – today: Synthesis fails with an RTL assertion error                                                         | 13        |

|     |          | 3.3.1.4    | Vivado 2016.4 – today: Resource consumption too high                                                                       | 13        |

|     |          | 3.3.1.5    | Vivado 2015.1 – today: Assertions and report messages are evaluated                                                        | not<br>14 |

|     |          | 3.3.1.6    | Vivado 2015.1 – today: ZC702_AXI_VIVADO example designate timing failures                                                  | า<br>14   |

|     |          | 3.3.1.7    | Vivado 2014.1 – today: Upgrading ZC702_AXI_VIVADO example results in warning on port differences                           | 14        |

|     |          | 3.3.1.8    | Vivado 2013.1 – today: EtherCAT IP Core is not part of the IF                                                              |           |

|     | 0.00     | 0          | Catalog                                                                                                                    | 15        |

|     | 3.3.2    | Solved     |                                                                                                                            | 16        |

|     |          | 3.3.2.1    | Vivado 2015.1 – today with EtherCAT IP Core before v3.00k Patch 3: ZC702_AXI_VIVADO example design constraints fa          | il16      |

|     |          | 3.3.2.2    | Vivado 2016.1 – 2016.3: Resource consumption too high, synthesis time is too high                                          | 16        |

|     |          | 3.3.2.3    | Vivado 2015.3 – 2015.4: EXCEPTION_ACCESS_VIOLATION during synthesis because of tristate drivers (crash)                    | N<br>16   |

|     |          | 3.3.2.4    | Vivado 2015.1 – 2015.4: Resource consumption too high, synthesis time is too high                                          | 17        |

|     |          | 3.3.2.5    | Vivado 2015.1: EtherCAT IP cores outside the Zynq block design fails in SDK (ZC702_AXI_VIVADO example design algebrated)   | so<br>17  |

|     |          | 3.3.2.6    | Vivado 2014.4: EtherCAT IP cores outside the Zynq block design fails in SDK (ZC702_AXI_VIVADO example design all affected) | so<br>17  |

|     |          | 3.3.2.7    | Vivado 2014.3: EXCEPTION_ACCESS_VIOLATION during synthesis (crash)                                                         | 18        |

|     |          | 3.3.2.8    | Vivado 2014.2 – 2014.3: Resource consumption too high                                                                      | 18        |

|     |          | 3.3.2.9    | Vivado 2014.1 – 2014.3: Tri-state drivers inside EtherCAT IP Core                                                          | 18        |

|     |          | 3.3.2.10   | Vivado 2014.1 – 2014.2: The resource consumption of the EtherCAT IP Core is too high                                       | 19        |

|     |          | 3.3.2.11   | Vivado 2013.2 – 2014.1: The ZC702 AXI Vivado example design is not synthesizable                                           | 19        |

|     |          | 3.3.2.12   | Vivado 2013.1 – 2013.2 with EtherCAT IP Core until V3.00f: License issue                                                   | IP<br>19  |

| 3.4 | ISE desi | gn tool co | mpatibility                                                                                                                | 20        |

| 3.5 | Known I  | SE/EDK/F   | PlanAhead 14.7 design flow issues                                                                                          | 21        |

|     | 3.5.1    | ISE: Cra   | sh in libSecurity_FNP.dll                                                                                                  | 21        |

|     | 3.5.2    | ISE/EDK    | (/PlanAhead: Additional BUFG inserted                                                                                      | 21        |

|   |          | required 21                                         | constraint |

|---|----------|-----------------------------------------------------|------------|

|   | 3.6      | MD5 checksums                                       | 22         |

| 4 | Appendix |                                                     | 24         |

|   | 4.1      | Support and service                                 | 24         |

|   |          | 4.1.1 Beckhoff's branch offices and representatives | 24         |

|   | 4.2      | Beckhoff headquarters                               | 24         |

BECKHOFF New Automation Technology

Overview

## 1 Overview

This document provides latest release notes, documentation addendum, supported IP Core design flows, and supported IP Core FPGA types for the following Beckhoff EtherCAT Slave Controllers:

- EtherCAT IP Core for Altera® FPGAs (up to V2.4.4 Patch 1 / V3.0.10 Patch 3)

- EtherCAT IP Core for AMD® (Xilinx)® FPGAs (up to V2.04e Patch 1 / V3.00k Patch 3)

Refer to the ESC data sheets for further information. The ESC data sheets are available from the Beckhoff homepage (http://www.beckhoff.com).

BECKHOFF New Automation Technology EtherCAT IP Core for Altera FPGAs

## 2 EtherCAT IP Core for Altera FPGAs

## 2.1 FPGA design tool compatibility

Table 1: EtherCAT IP Core for Altera FPGAs compatibility with Altera Quartus tools

| IP Core<br>version |         |                 |                               |            |                    |                    |            |     |      |      | Prime | Stand | ard / N     | IOS EI | DS vers     | sion con | npatibili         | ity               |                            |                            |               | Quartus Prime Pro<br>version<br>compatibility |               |               |

|--------------------|---------|-----------------|-------------------------------|------------|--------------------|--------------------|------------|-----|------|------|-------|-------|-------------|--------|-------------|----------|-------------------|-------------------|----------------------------|----------------------------|---------------|-----------------------------------------------|---------------|---------------|

|                    |         | SoPC<br>Builder | Qsys/<br>Platform<br>Designer | 5.1<br>SP2 | 6.1-<br>7.1<br>SP1 | 7.2<br>SP2-<br>8.0 | 9.0<br>SP1 | 9.1 | 10.0 | 10.1 | 11.0  |       | 12.0<br>SP1 |        | 13.0<br>SP1 | 13.1.4   | 14.0 <sup>1</sup> | 14.1 <sup>1</sup> | 15.0-<br>17.0 <sup>1</sup> | 17.1-<br>19.1 <sup>1</sup> | 20.1-<br>23.1 | 16.0-<br>17.0                                 | 17.1-<br>19.1 | 20.1-<br>23.4 |

| 1.0.0              | 7/2006  | •               | -                             | •          |                    |                    |            |     |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 1.1.0              | 11/2006 | •               | -                             | •          |                    |                    |            |     |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 1.1.1              | 1/2007  | •               | -                             | •          | •                  |                    |            |     |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.0.0              | 8/2007  | •               | -                             | •          | •                  |                    |            |     |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.2.0              | 6/2008  | •               | -                             | •          | •                  | •                  |            |     |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.2.1              | 6/2009  | •               | -                             | -          | -                  | -                  | •          |     |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.3.0              | 12/2009 | •               | -                             | -          | -                  | -                  | -          | •   |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.3.1              | 2/2010  | •               | -                             | -          | -                  | -                  | -          | •   |      |      |       |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.3.2              | 3/2010  | •               | -                             | -          | -                  | -                  | -          | •   | •    | •    | 0     |       |             |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.4.0              | 3/2011  | •               | •                             | -          | -                  | -                  | -          | -   | -    | •    | •     | •     | -           |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.4.0 Patch 5      | 6/2012  | •               | •                             | -          | -                  | -                  | -          | -   | -    | •    | •     | •     | •           |        |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 2.4.3              | 7/2013  | •               | •                             | -          | -                  | -                  | -          | -   | -    | •    | •     | •     | •           | •      | •           | •        | •                 |                   |                            |                            |               |                                               |               |               |

| 2.4.4              | 1/2015  | •               | •                             | -          | -                  | -                  | -          | -   | -    | •    | •     | •     | •           | •      | •           | •        | •                 | •                 |                            |                            |               |                                               |               |               |

| 2.4.4 Patch 1      | 6/2016  | •               | •                             | -          | -                  | -                  | -          | -   | -    | •    | •     | •     | •           | •      | •           | •        | •                 | •                 |                            |                            |               |                                               |               |               |

| 3.0.0              | 3/2013  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      |             |          |                   |                   |                            |                            |               |                                               |               |               |

| 3.0.1              | 3/2013  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      | •           |          |                   |                   |                            |                            |               |                                               |               |               |

| 3.0.2              | 5/2013  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      | •           | •        |                   |                   |                            |                            |               |                                               |               |               |

| 3.0.5              | 2/2014  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      | •           | •        |                   |                   |                            |                            |               |                                               |               |               |

| 3.0.6              | 4/2014  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      | •           | •        | •                 |                   |                            |                            |               |                                               |               |               |

| 3.0.9              | 9/2014  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      | •           | •        | •                 | •                 |                            |                            |               |                                               |               |               |

| 3.0.9 Patch 1      | 11/2014 | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    | •     | •     | •           | •      | •           | •        | •                 | •                 |                            |                            |               |                                               |               |               |

| 3.0.10             | 1/2015  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    |       |       |             |        |             | •        | •                 | •                 | •                          |                            |               | •                                             |               |               |

| 3.0.10 Patch 2     | 5/2019  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    |       |       |             |        |             | •        | •                 | •                 | •                          | •                          |               | •                                             | •             |               |

| 3.0.10 Patch 3     | 7/2020  | •               | •                             | -          | -                  | -                  | -          | -   | -    | -    |       |       |             |        |             |          |                   |                   | •                          | •                          | •             | •                                             | •             | •             |

Table 2: Tool compatibility legend

| Symbol | Description                                           |

|--------|-------------------------------------------------------|

| •      | Compatible (maybe solved issues with example designs) |

| 0      | Compatible, issues with some example designs          |

| -      | Incompatible                                          |

|        | Not tested                                            |

<sup>&</sup>lt;sup>1</sup> Cyclone III devices are not supported anymore by Quartus, corresponding example designs cannot be synthesized. Refer to known issues for more details.

BECKHOFF New Automation Technology EtherCAT IP Core for Altera FPGAs

## 2.2 FPGA device compatibility

Starting with V2.4.0 Patch 5, the family support check of the MegaWizard plugin has been turned off (a license update is now sufficient for new FPGA families).

Table 3: EtherCAT IP Core for Altera FPGAs compatibility with Altera FPGAs

| IP Core<br>version | Cyclone | Cyclone<br>II | Cyclone<br>III | Cyclone<br>III LS | Cyclone IV E / Cyclone IV GX | Cyclone<br>V /<br>Cyclone<br>V SoC | Cyclone<br>10 GX /<br>LP | Agilex<br>5 | Agilex<br>7 | Arria<br>GX | Arria<br>II GX | Arria<br>II GZ | Arria<br>V /<br>Arria<br>V GZ | Arria<br>10 | Stratix/<br>Stratix<br>II |   | Stratix<br>III | Stratix<br>IV | Stratix<br>V | Stratix<br>10 | Intel<br>Atom<br>E6x5C | MAX<br>10 |

|--------------------|---------|---------------|----------------|-------------------|------------------------------|------------------------------------|--------------------------|-------------|-------------|-------------|----------------|----------------|-------------------------------|-------------|---------------------------|---|----------------|---------------|--------------|---------------|------------------------|-----------|

| 1.0.0              | •       | •             | -              | -                 | -                            | -                                  | -                        |             |             | -           | -              | -              | -                             | -           | •                         | - | -              | -             | -            |               | -                      | -         |

| 1.1.0              | •       | •             | -              | -                 | -                            | -                                  | -                        |             |             | -           | -              | -              | -                             | -           | •                         | - | -              | -             | -            |               | -                      | -         |

| 1.1.1              | •       | •             | -              | -                 | -                            | -                                  | -                        |             |             | -           | -              | -              | -                             | -           | •                         | - | -              | -             | -            |               | -                      | -         |

| 2.0.0              | •       | •             | •              | -                 | -                            | -                                  | -                        |             |             | •           | -              | -              | -                             | -           | •                         | • | •              | -             | -            |               | -                      | -         |

| 2.2.0              | •       | •             | •              | -                 | -                            | -                                  | -                        |             |             | •           | -              | -              | -                             | -           | •                         | • | •              | •             | -            |               | -                      | -         |

| 2.2.1              | •       | •             | •              | -                 | -                            | -                                  | -                        |             |             | •           | •              | -              | -                             | -           | •                         | • | •              | •             | -            |               | -                      | -         |

| 2.3.0              | •       | •             | •              | •                 | •                            | -                                  | -                        |             |             | •           | •              | -              | -                             | -           | •                         | • | •              | •             | -            |               | -                      | -         |

| 2.3.1              | •       | •             | •              | •                 | •                            | -                                  | -                        |             |             | •           | •              | -              | -                             | -           | •                         | • | •              | •             | -            |               | -                      | -         |

| 2.3.2              | •       | •             | •              | •                 | •                            | -                                  | -                        |             |             | •           | •              | -              | -                             | -           | •                         | • | •              | •             | -            |               | -                      | -         |

| 2.4.0              | •       | •             | •              | •                 | •                            | -                                  | -                        |             |             | •           | •              | •              | -                             | -           | •                         | • | •              | •             | •            |               | •                      | -         |

| 2.4.0 Patch 5      | •       | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             | •                         | • | •              | •             | •            |               | •                      | •         |

| 2.4.3              | •       | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             | •                         | • | •              | •             | •            |               | •                      | •         |

| 2.4.4              | •       | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             | •                         | • | •              | •             | •            |               | •                      | •         |

| 2.4.4 Patch 1      | •       | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             | •                         | • | •              | •             | •            |               | •                      | •         |

| 3.0.0              |         | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             |                           | • | •              | •             | •            |               | •                      | •         |

| 3.0.1              |         | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             |                           | • | •              | •             | •            |               | •                      | •         |

| 3.0.2              |         | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             |                           | • | •              | •             | •            |               | •                      | •         |

| 3.0.5              |         | •             | •              | •                 | •                            | •                                  |                          |             |             | •           | •              | •              | •                             |             |                           | • | •              | •             | •            |               | •                      | •         |

| 3.0.6              |         |               | •              | •                 | •                            | •                                  |                          |             |             |             | •              | •              | •                             |             |                           |   | •              | •             | •            |               | •                      | •         |

| 3.0.9              |         |               | •              | •                 | •                            | •                                  |                          |             |             |             | •              | •              | •                             |             |                           |   | •              | •             | •            |               | •                      | •         |

| 3.0.9 Patch 1      |         |               | •              | •                 | •                            | •                                  |                          |             |             |             | •              | •              | •                             |             |                           |   | •              | •             | •            |               | •                      | •         |

| 3.0.10             |         |               | •              | •                 | •                            | •                                  | •                        |             |             |             | •              | •              | •                             | •           |                           |   | •              | •             | •            |               | •                      | •         |

| 3.0.10 Patch 2     |         |               | •              | •                 | •                            | •                                  | •                        |             |             |             | •              | •              | •                             | •           |                           |   | •              | •             | •            |               | •                      | •         |

| 3.0.10 Patch 3     |         |               | •              | •                 | •                            | •                                  | •                        | •           | •           |             | •              | •              | •                             | •           |                           |   | •              | •             | •            | •             | •                      | •         |

Table 4: FPGA compatibility legend

| Symbol | Description  |

|--------|--------------|

| •      | Compatible   |

| -      | Incompatible |

|        | Not tested   |

## 2.3 FPGA device license support

Every license for the EtherCAT IP Core contains restrictions on supported FPGA devices. All FPGA device families which have license support at the date when the license is generated are unlocked. The following table shows the dates of introduction of the FPGA license support. All EtherCAT IP Core licenses which are generated past the date will include the marked FPGA devices.

Table 5: EtherCAT IP Core for Altera FPGAs license support

| First date<br>of license<br>support | Cyclone/<br>Cyclone<br>II | Cyclone<br>III | Cyclone<br>III LS | Cyclone<br>IV E | Cyclone<br>IV GX | Cyclone<br>V /<br>Cyclone<br>V SoC | 10 GX / | Agilex<br>5 | Agilex<br>7 | Arria<br>GX | Arria<br>II GX | Arria<br>II GZ | Arria<br>V | Arria<br>V GZ | Arria<br>10 | Stratix/<br>Stratix<br>GX/<br>Stratix<br>II /<br>Stratix<br>II GX | Stratix<br>III | Stratix<br>IV | Stratix<br>V | Stratix<br>10 | Intel<br>Atom<br>E6x5C | MAX10 |

|-------------------------------------|---------------------------|----------------|-------------------|-----------------|------------------|------------------------------------|---------|-------------|-------------|-------------|----------------|----------------|------------|---------------|-------------|-------------------------------------------------------------------|----------------|---------------|--------------|---------------|------------------------|-------|

| Initial                             | •                         | -              | -                 | -               | -                | -                                  | -       | -           | -           | -           | -              | -              | -          | -             | -           | •                                                                 | -              | -             | -            | -             | -                      | -     |

| 2007-03-28                          | •                         | •              | -                 | -               | -                | -                                  | -       | -           | -           | -           | -              | -              | -          | -             | -           | •                                                                 | •              | -             | -            | -             | -                      | -     |

| 2007-08-16                          | •                         | •              | -                 | -               | -                | -                                  | -       | -           | -           | •           | -              | -              | -          | -             | -           | •                                                                 | •              | -             | -            | -             | -                      | -     |

| 2008-06-03                          | •                         | •              | -                 | -               | -                | -                                  | -       | -           | -           | •           | -              | -              | -          | -             | -           | •                                                                 | •              | •             | -            | -             | -                      | -     |

| 2009-05-27                          | •                         | •              | -                 | -               | -                | -                                  | -       | -           | -           | •           | •              | -              | -          | -             | -           | •                                                                 | •              | •             | -            | -             | •                      | -     |

| 2009-07-02                          | •                         | •              | •                 | -               | -                | -                                  | -       | -           | -           | •           | •              | -              | -          | -             | -           | •                                                                 | •              | •             | -            | -             | •                      | -     |

| 2009-11-27                          | •                         | •              | •                 | -               | •                | -                                  | -       | -           | -           | •           | •              | -              | -          | -             | -           | •                                                                 | •              | •             | -            | -             | •                      | -     |

| 2010-06-07                          | •                         | •              | •                 | •               | •                | -                                  | -       | -           | -           | •           | •              | -              | -          | -             | -           | •                                                                 | •              | •             | -            | -             | •                      | -     |

| 2011-03-22                          | •                         | •              | •                 | •               | •                | -                                  | -       | -           | -           | •           | •              | •              | •          | -             | -           | •                                                                 | •              | •             | •            | -             | •                      | -     |

| 2012-06-25                          | •                         | •              | •                 | •               | •                | •                                  | -       | -           | -           | •           | •              | •              | •          | -             | -           | •                                                                 | •              | •             | •            | -             | •                      | -     |

| 2013-02-15                          | •                         | •              | •                 | •               | •                | •                                  | -       | -           | -           | •           | •              | •              | •          | •             | -           | •                                                                 | •              | •             | •            | -             | •                      | -     |

| 2014-05-06                          | •                         | •              | •                 | •               | •                | •                                  | -       | -           | -           | •           | •              | •              | •          | •             | -           | •                                                                 | •              | •             | •            | -             | •                      | •     |

| 2014-05-08                          | •                         | •              | •                 | •               | •                | •                                  | -       | -           | -           | •           | •              | •              | •          | •             | •           | •                                                                 | •              | •             | •            | -             | •                      | •     |

| 2017-04-20                          | •                         | •              | •                 | •               | •                | •                                  | •       | -           | -           | •           | •              | •              | •          | •             | •           | •                                                                 | •              | •             | •            | -             | •                      | •     |

| 2022-02-17                          | •                         | •              | •                 | •               | •                | •                                  | •       | -           | -           | •           | •              | •              | •          | •             | •           | •                                                                 | •              | •             | •            | •             | •                      | •     |

| 2022-03-24                          | •                         | •              | •                 | •               | •                | •                                  | •       | -           | •           | •           | •              | •              | •          | •             | •           | •                                                                 | •              | •             | •            | •             | •                      | •     |

| 2023-10-21                          | •                         | •              | •                 | •               | •                | •                                  | •       | •           | •           | •           | •              | •              | •          | •             | •           | •                                                                 | •              | •             | •            | •             | •                      | •     |

Table 6: License support legend

| Symbol | Description   |

|--------|---------------|

| •      | Supported     |

| _      | Not supported |

#### 2.4 Known design flow issues

## 2.4.1 Active (at least until Quartus Prime Standard 23.1/Quartus Prime Pro 23.4)

#### 2.4.1.1 Quartus Prime 21.1 – today: DE2\_115 example designs are missing component altera\_avalon\_lcd\_16207

Quartus Platform designer reports this error message:

```

Error: DE2 115 EtherCAT NIOS RGMII QSYS.lcd 0: Component altera avalon lcd 16207 11.0 not found or could not be instantiated

```

This IP is no longer part of Quartus.

#### Solution

This IP can be replaced by the "16x2 Character Display" IP – but the driver has much less functionality. Therefore, the example software must be changed, to achieve a proper LCD output. To get the hardware synthesizable, follow these steps to update the system:

- 1. Remove the lcd 0 IP

- 2. Add the new "16x2 Character Display", set display cursor configuration to "none"

- 3. Change IP instance name to "lcd 0", connect to the Avalon bus (same bus/clock/reset as sysid).

- 4. Export the signals, rename external signal name to "lcd 0 external"

- 5. Assign base address 0x00091090

- 6. In the Quartus top level VHDL file, rename declaration and connection of "lcd\_0\_external\_E" to "lcd\_0\_external\_EN", since this IP signal name has changed

- 7. To make the LCD show useful information, refer to the documentation of the IP and change the example software appropriately. This step is optional, you can ignore LCD output without updating.

#### 2.4.1.2 Quartus Prime Pro – today: Critical warnings about ignored initial state in some state machines

Quartus Prime Pro may report these critical warning messages:

```

Critical Warning(19434): Ignored initial state "QFS3759.ffs3754" on state machine "QFS3759". The state machine powers up to state "QFS3759.rfs3755" due to asynchronous reset Critical Warning(19434): Ignored initial state "QFS3759.gfs3792" on state machine "QFS3759". The state machine powers up to state "QFS3759.ofs3793" due to asynchronous reset Critical Warning(19434): Ignored initial state "QFS3759.ffs3754" on state machine "QFS3759". The state machine powers up to state "QFS3759.mfs4567" due to asynchronous reset Critical Warning(19434): Ignored initial state "QFS3759.ffs3754" on state machine "QFS3759". The state machine powers up to state "QFS3759.qfs4222" due to asynchronous reset

```

The EtherCAT IP Core does not use, or contain, register initialization at start-up for synthesis, instead, it uses an asynchronous reset for initialization.

#### Solution

These warning messages can be ignored. The power up states due to asynchronous resets are the ones which are described in the source code.

#### 2.4.1.3 Quartus Prime Pro 17.0 – today: Upgrade to Qsys Pro/Platform Designer Pro fails due to missing simulation support

Upgrading a project with EtherCAT IP Core from Qsys to Qsys Pro/Platform designer Pro fails with an error message

Error: EtherCAT 0: EtherCAT does not support generation for Verilog Simulation. Generation is available for: Quartus Synthesis.

This is related to simulation of the EtherCAT IP Core, which is not supported.

#### Solution

Please open the upgraded system in Qsys Pro, and generate the HDL without enabling simulation model creation.

#### 2.4.1.4 Quartus Prime Standard/Pro 16.1 – today: Windows setup does not integrate the EtherCAT IP Core into the Quartus IP catalog

The windows setup does not detect installations of Quartus Prime Standard/Pro since 16.1, so it does not offer integrating the EtherCAT IP Core into these versions. This is caused by the EtherCAT IP Core setup, which is a 32 bit executable. It cannot locate 64 bit applications, so Quartus is not found.

#### Solution

Integrate the EtherCAT IP Core into Quartus manually by copying the <IPInst\_dir>\quartus\_add\\content into your Quartus installation folder, according to the EtherCAT IP Core data sheet (section III, chapter 3.6).

#### 2.4.1.5 Quartus 14.0 - today: Cyclone III example designs are not synthesizable

Cyclone III devices are not supported anymore by Quartus 14, corresponding example designs cannot be synthesized.

#### Solution

None. Use previous Quartus versions.

#### 2.4.1.6 TimeQuest with EtherCAT IP Core V3.0.x: Recovery timing violation inside the EtherCAT IP Core from 25 MHz rising edge to 100 MHz falling edge (5 ns)

In rare cases, a recovery timing violation occurs inside the EtherCAT IP Core between two flip-flops. The start flip-flop is called HNR3530 (using the 25 MHz clock at the rising edge), and the end flip-flop is called BNR3543.ACL2024 (using the 100 MHz clock at the falling edge). Quartus infers a CLKCTRL instance on the path, which sometimes causes the recovery timing violation.

#### Solution

To:

Quartus can be forced to connect both flip-flops individually, without using the CLKCTRL instance. All other targets of the CLKCTRL will remain untouched. Please use the Assignment Editor to add this assignment:

From: \*ETHERCAT IPCORE V2:ethercat 0|ETHERCAT CORE:\CORE INST:CORE INST|OCL3344:OCL3344|HNR3530\*

\*ETHERCAT IPCORE V2:ethercat 0|ETHERCAT CORE:\CORE INST:CORE INST|OCL3344:OCL3344|BNR3543.ACL2024\*

Assignemt Name: Global Signal

Value: Off Enabled: Yes

#### 2.4.1.7 Qsys with EtherCAT IP Core V2.x.x: Avalon read error

With Qsys, a 32 bit read access to the EtherCAT IP Core might have gaps between the bytes. The prefetch feature (*Data width of smallest Avalon Master* is set to 2 or 4 byte), which is available in EtherCAT IP Core versions before V3.0.0, does not support these gaps, read errors occur as a consequence.

#### Solution

Set the configuration option Data width of smallest Avalon Master to 1 byte, prefetch is disabled then.

BECKHOFF New Automation Technology EtherCAT IP Core for Altera FPGAs

#### 2.4.2 **Solved**

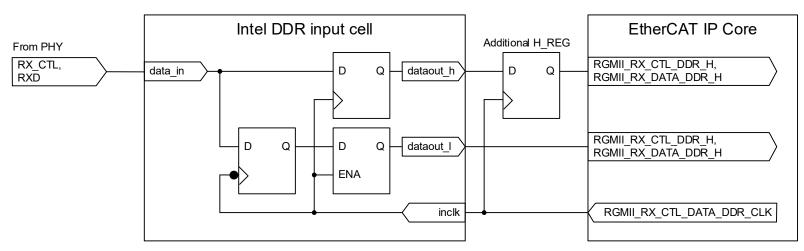

#### 2.4.2.1 EtherCAT IP Core before V3.0.10 Patch 3: DE2-115 NIOS RGMII example design is missing a register for DDR input signals

The EtherCAT IP Core evaluates RGMII DDR input signals at the rising clock edge, and it expects that the DDR\_H input was sampled before the DDR\_L input. For RX\_CTL, this means that DDR\_H contains RX\_DV, while DDR\_L contains RX\_ER for the same receive clock cycle.

The DE2-115 NIOS RGMII example design uses an Altera DDR input cell which uses a reversed DDR\_L/DDR\_H ordering. Due to a certain behaviour of the PHYs on this boards, this will not cause problems, but using the example design for other PHYs can result in receive errors.

#### Solution

An additional register has to be added to the DDR H path for each RX CTL/RX DATA[3:0] signal, according to the following schematic:

Figure 1: Additional H\_REG for RGMII inputs using Altera DDR input cells

Example code for the additional H\_REG for one port (duplicate and update port numbers for additional ports):

## 2.4.2.2 Quartus Prime Standard 16.0 – today with EtherCAT IP Core before V3.0.10 Patch 3: DE2-115 MII/RGMII example designs: synthesis fails because of an additional ALTPLL signal

Synthesis fails because Qsys does no longer generate the ALTPLL phasedone signal, when this feature is not used. Previous versions of Quartus generated that signal, so it was referenced by the example designs.

#### Solutio

Delete the signal altpll 0 phasedone conduit export from the component declaration and instantiation in the top level file.

## 2.4.2.3 Quartus 14.0 – today with EtherCAT IP Core before V3.0.10 Patch 1: Cyclone IV DBC4CE55 with NIOS example design PLL cannot be upgraded or edited

The PLL IP cannot be upgraded/edited because it contains a Cyclone III device as the target device family, although a Cyclone IV device is actually used:

```

Error (14921): Error upgrading IP component "pll.vhd".

```

#### Solution

Please change the device family in the file pll.vhd from

```

"Cyclone III" to "Cyclone IV E"

```

There are three occurrences of "Cyclone III", just replace all of them by "Cyclone IV E", and upgrade or edit the pll.vhd IP afterwards.

## 2.4.2.4 MAX10 with EtherCAT IP Core V2.4.0 – V3.0.10 Patch 1: Some configuration modes are not possible with EtherCAT IP Core memory initialization

The EtherCAT IP core uses memory initialization for the User RAM (0x0F80:0x0FFF), but only for debugging purposes (display selected ESC features). This memory initialization prevents the usage of some MAX10 configuration modes which do not support memory initialization.

#### Solution

A modified EtherCAT IP Core without memory initialization is available upon request.

#### 2.4.2.5 Quartus Prime Pro 16.0 – 21.3: Assertions and report messages are not evaluated

Quartus Prime Pro does not evaluate assertions and report messages anymore, even if they are based on constants or generics. As a result, the messages shown by the EtherCAT IP core source code (text configuration box) are no longer visible. Additionally, assertions resulting in errors or failures are no longer causing the synthesis to fail, thus, illegal configurations might become synthesized to dysfunctional logic. This is unlikely to happen since the configuration interface prevents illegal configurations, but manual changes might cause them.

#### Solution

Since Quartus Prime Pro 21.4, assertions can be enabled in compiler settings: "Enable VHDL static assertion support".

#### 2.4.2.6 Quartus Prime Standard 16.0.0: DE2-115 MII/RGMII example designs: ALTPLL cannot be generated

Generating the Qsys fails with an error caused by the ALTPLL:

```

Error (12252): Altpll 0: Port phasecounterselect has width 4 in TCL, but 3 in the design file

```

This issue is caused by Quartus, which incorrectly expects a signal width of 4 for the unused port phasecounterselect. This issue has already been reported to Altera.

#### Solution

Update to Quartus Prime Standard 16.0.1 (partially solves the issue). An intermediate solution is to extend the ALTPLL TCL file located in

<Quartus installation folder>\16.0\ip\altera\sopc\_builder\_ip\altera\_avalon\_altpll\altera\_avalon\_altpll\_hw.tcl

with an additional condition for the device family (row 339 ff.):

```

set device_family [get_parameter_value INTENDED_DEVICE_FAMILY]

if { $device_family == "MAX10" || $device_family == "MAX 10" || $device_family == "Cyclone IV E"} {

set phasectrsel_width 3

} else {

set phasectrsel_width 4

}

```

## 2.4.2.7 Quartus 14.0: EtherCAT IP Core V3.0.0-V3.0.6: DE2-115 example designs are not working

The DE2-115 example designs are not working when synthesized using Quartus 14.0 (no communication, no display). The reason is that the PLL remains in reset state, because the areset input pin is not connected. Quartus 14.0 seems to use a different input value for this signal, causing the reset to be active all the time.

#### Solution

Open Qsys, export the altpll\_0 module's areset\_conduit signal, and connect it to GND. The warning regarding this conduit disappears.

## 2.5 MD5 Checksums

Table 7: MD5 checksums

| IP Core version | Installation file                    |                                                                                                          | EtherCAT_IPCore.vhd              | EtherCAT_IPCore_TOP.vhd          | EtherCAT_IPCore.ocp              |

|-----------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 1.0.0           | Linux:<br>Windows Setup:<br>Solaris: | D1D0C450B8F043D38C2277F0D92EE941<br>12AF6DE282CAACED8ACDCA5FE66906EE<br>22569688EAB18E96FC706E755D4746B2 | 2B587DF40D9CC6E9138122B9CC541C50 | -                                | -                                |

| 1.1.0           | Linux:<br>Windows Setup:<br>Solaris: | D38CF74CDE42193CDC851336E4D48134<br>395215C741F9A62FED01B22B97988B79<br>173BB13DA241EDE44ECD213AE144D7EF | 886CF05AC182CFDC03DAED1431C1CEDB | -                                | 4CD1C6E5BAAC6B959E3A220A6A60E4BE |

| 1.1.1           | Linux:<br>Windows Setup:<br>Solaris: | 324D9BE05EB0D1A2C5796845B008D2B6<br>776C9257CB2A454391B61B7CD38AE8F4<br>7FC91870F69AEAE49AB2A2FD97E5A2F5 | E845C4FC91D3316E2B028129937E875C | -                                | DC2FA3CA77D7EE1212D0F3D147AB0C30 |

| 2.0.0           | Linux:<br>Windows Setup:<br>Solaris: | B3E095764023F4EF6C399B16AC213AC8<br>EDCB8A9C51030947E5FA1B2C2B6D7510<br>242BD90B56437E61E369B0DCFD7A0563 | 0315BEF8034EE4E5BC2B17AA0EF7A28B | -                                | 90EB2FF0057380F9A815F7E7180E112C |

| 2.2.0           | Linux:<br>Windows Setup:<br>Solaris: | 069D2FF2D89BA4AF95E6C09DE30F3A29<br>17B6ABBFC9A2BA37D120FC0E41E6EB51<br>1D06CCE0DC542CDB6C3185E79DDFC24C | 74BBDCE9FABFC8C86785A26CD03F3F79 | -                                | 7846AEC73A78481D25635572D7747278 |

| 2.2.1           | Linux:<br>Windows Setup:<br>Solaris: | C4566CF9983B4E7AA1366168D0F36124<br>364B0C44866CDBF7B57E738EF3C9DF4F<br>96D5D8CAC8B843725F60D996CE94B6EE | 60DB043F690F5FEFF4E3BADD8FBD9CA6 | -                                | 46F3936B35684565055D7EC119C92617 |

| 2.3.0           | Linux:<br>Windows Setup:<br>Solaris: | 60610D11ED5D8B2A711FACFFEE658731<br>14EAF65D006D79CD3187C838BB17303D<br>946855E035A0FE774E68BD06E0581EBA | A04286DC7280A99D46F24234BA0FAD4D | -                                | 2B31E75D24AB4A3E15EBD1CEB71CF0C7 |

| 2.3.1           | Linux:<br>Windows Setup:<br>Solaris: | 41883CEF9C07A98A5D3DB022BE265438<br>CCA866485E1106A7B55C4E3011A38A4E<br>C5470241D9AEA775761085B1A18B3DB5 | 5E64B409234AF3FAC47479912C717A32 | -                                | 5EDCFE8B16A867F76AA3BE50957BAFDF |

| 2.3.2           | Linux:<br>Windows Setup:<br>Solaris: | 12887B6A71603E94A5288210453A5A76<br>AF304B9200F4D96F890AFC90B8249C54<br>ADF1F4F197A0BE62BE84A742221239A4 | CBC425E967A12E11E2C8FE9A5D86405B | -                                | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.0           | Linux:<br>Windows Setup:             | 6A5CCAD8D9960C0EB502B9AA3FB738E8<br>E67ED1EF67A6F16B1B49E138D57FBB67                                     | 2A8778F0A8DAAEAE91DB5A3048873885 | 337A37409F0E1E52E79CD85409239F80 | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.0 Patch 1   | Linux:<br>Windows Setup:             | AF3BE8493B5988B8296345FDCCC25858<br>E10582BFE77B1928E85D1352439AEA6F                                     | 2A8778F0A8DAAEAE91DB5A3048873885 | 337A37409F0E1E52E79CD85409239F80 | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.0 Patch 2   | Linux:<br>Windows Setup:             | 6D4951038B8BCF5C706463DE347AFC99<br>2851B75D8B9E8265EDC19CD516519B10                                     | 2A8778F0A8DAAEAE91DB5A3048873885 | 337A37409F0E1E52E79CD85409239F80 | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.0 Patch 3   | Linux:<br>Windows Setup:             | 1E14526833B2611B76BD05651DBC485B<br>5560ED46EC0924654F5DBB3AA9BACD92                                     | 2A8778F0A8DAAEAE91DB5A3048873885 | 337A37409F0E1E52E79CD85409239F80 | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.0 Patch 4   | Linux:<br>Windows Setup:             | 437B368ED2DA42ACA8D5D95BFA798D9A<br>9D91A011346324CD25269422E84B5EBD                                     | 2A8778F0A8DAAEAE91DB5A3048873885 | 337A37409F0E1E52E79CD85409239F80 | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.0 Patch 5   | Linux:<br>Windows Setup:             | B1B335CB6EDC0932FB8B441C2FDDF888<br>7BD8EEF74B8BA11DA88832351506090C                                     | 2A8778F0A8DAAEAE91DB5A3048873885 | 337A37409F0E1E52E79CD85409239F80 | 0947B2C6D54A35A288ADBA2615AB0B5D |

| 2.4.3           | Linux:<br>Windows Setup:             | 8488E660257A22863F870CABAAA48EB5<br>567EA5895550BD17E58AB2D164CF2A07                                     | C01FE074B35C2F1AC80DB2F01F6C103B | 627B7F77F22780F5BD675F5840830B08 | A9C68DF57265D6C83837E1514D1B17C2 |

| 2.4.4           | Linux:<br>Windows Setup:             | C5DD598B195B6F61C3229F901979739A<br>3890A9DA4CB2144C3594E5CE9A4296A2                                     | 441C076EA8333C9496A0EFBB37E2C3A7 | 84C952B1442AE1935E1DE573E4CB95D8 | A9C68DF57265D6C83837E1514D1B17C2 |

| 2.4.4 Patch 1   | Linux:<br>Windows Setup:             | 465985CD8FBA1017C25956DA25855F4B<br>C9EFB33E6F063DCA80A48EB9F7F63781                                     | 441C076EA8333C9496A0EFBB37E2C3A7 | 84C952B1442AE1935E1DE573E4CB95D8 | A9C68DF57265D6C83837E1514D1B17C2 |

| IP Core version | Installation file        |                                                                      | EtherCAT_IPCore.vhd              | EtherCAT_IPCore_TOP.vhd          | EtherCAT_IPCore.ocp              |

|-----------------|--------------------------|----------------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 3.0.0           | Linux:<br>Windows Setup: | 388B42C9FBEA8ECCD342B56842E715C8<br>617548350798372391D46E44FAFDFB0F | ADA5C6DE4BDCA4A4F0E09DE36E0DC88E | 9BAB935BC465767E19AED2C595239DA2 | 1099F8C3073EC879C36F8BD1AF7DB788 |

| 3.0.1           | Linux:<br>Windows Setup: | 9513ED2AB809654362C6EE1A32F53165<br>FBC35EBA4251824C37CE629FF7BA76C3 | 2367AEC85AFD1210301D5A60A083C725 | 8C2FA562028D97B0A9A50389F3586B36 | 1099F8C3073EC879C36F8BD1AF7DB788 |

| 3.0.2           | Linux:<br>Windows Setup: | 44AEAE95BA804D8198554A4C5DE7D225<br>7091E7B412794DEDF279571492836743 | 0E3F449BD673A9419156968406BDD1C8 | 3E8C73383C020EDA07D42DD2F1753C1D | 1099F8C3073EC879C36F8BD1AF7DB788 |

| 3.0.5           | Linux:<br>Windows Setup: | 2D9F984A740026E25894B20D778FBE2B<br>DDACF189B3DA7B5B07DE0A48C318B60C | C9B95CDEF4617A23B5B9FA2420174003 | FF01D708A668A75FC03099AC8CA2374B | 1099F8C3073EC879C36F8BD1AF7DB788 |

| 3.0.6           | Linux:<br>Windows Setup: | 3A4CB986424EB7FFE9C2135189B62B5F<br>E8174A0A7659F1A4E065916AF621BC7A | 6ED4389E58DD2495219E67A466AF4AB3 | 2F5C0B16572BD475F67BAEA1B279DE88 | C29B6ED1F91E5A438D91EC02D44296FB |

| 3.0.9           | Linux:<br>Windows Setup: | 46E52598159846B542CB1C17EAA4E54A<br>F03912C7B878168636D51B2727A911F4 | AE0072D4778EB09104021E0B658A3973 | 3113D9903B1FA03366A24979A63BF0F3 | 42AF256EA5C2A0AB2A2C212CE3110027 |

| 3.0.9 Patch 1   | Linux:<br>Windows Setup: | 177794354C51BCCFDA78CE0359D85DD2<br>E52F9038DA2A66AAE763C8F72353B4C9 | 42C87C693592048F97CE739CE7069F9D | 4EC1B9349A7E4835745F66192AF64E22 | 42AF256EA5C2A0AB2A2C212CE3110027 |

| 3.0.10          | Linux:<br>Windows Setup: | D26E85BC55750E12095E9D805D9563A8<br>821D6D5C9613E7F2938AEA60C576D7E7 | 2271C94E27FD58877D7201E65907BFBB | 232B26C1A1CE1581864D259C083CAC61 | 42AF256EA5C2A0AB2A2C212CE3110027 |

| 3.0.10 Patch 1  | Linux:<br>Windows Setup: | 97BEACAC5B513FC537243A89DD29BA77<br>BBF3646F63CA716F228A638F1269A980 | B795DAFBF89EEAF6ECBE34E1E19BDECB | 82DCDFF5AE4F029518E9C4ACA12841DE | 42AF256EA5C2A0AB2A2C212CE3110027 |

| 3.0.10 Patch 2  | Linux:<br>Windows Setup: | 7CB3223F3C342840FC0995EEECB1B55C<br>2D6F92E7F17344D67F56B847C4BE76DB | 9B9AD989A0B28E03454B39F3EB8CF2D3 | 777330A73D5449DABD2E8939F4700F35 | 42AF256EA5C2A0AB2A2C212CE3110027 |

| 3.0.10 Patch 3  | Linux:<br>Windows Setup: | A197C4D15E80F8798DD1ECBC435D2FAA<br>4DB10E710014498B0BF2BDEDAC988102 | 6E321B33F065B61DECC9458420EEDA2D | 0349F61D9CB0287052ED0B0DB8B8C53B | 42AF256EA5C2A0AB2A2C212CE3110027 |

**BECKHOFF** New Automation Technology

## 3 EtherCAT IP Core for AMD FPGAs

## 3.1 Vivado/Vitis design tool compatibility

Table 8: EtherCAT IP Core for AMD FPGAs compatibility with AMD Vivado/Vitis design flow tools

| IP Core version | Release<br>date | 2012.3 | 2013.1 | 2014.1 | 2014.2 | 2014.3 | 2014.4 | 2015.1 | 2015.2      | 2017.1 | 2020.2 |